Also…wrt his Antenna design for space connectivity:

MagPi Issues 88:

& 89:

Remember dont just download the free .pdf… subscribe & provide support

Assessment of impact and potential of emerging ‘open’ standards in Telecom Infrastructure

https://www.eetimes.com/is-the-telecom-infrastructure-market-ready-for-openness/

Is the Telecom Infrastructure Market Ready for Openness?

https://www.nature.com/articles/s41586-019-1666-5

Review of Google’s 54 QuBit ‘Sycamore’ Quantum Compute element

- Article

- Published: 23 October 2019

Quantum supremacy using a programmable superconducting processor

designLines

Internet Of Things Designline

5 Pivotal Events in IoT and Embedded

https://www.eetimes.com/5-pivotal-events-in-iot-and-embedded/

UWB, Connectivity, ARM Customisation, Open Source Security, RISC-V…

07 Jan 2020 | Geneva

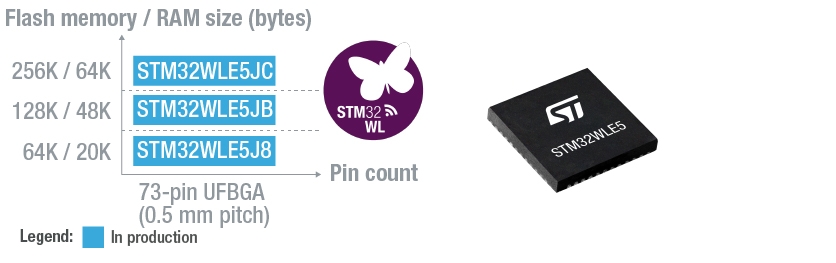

STMicroelectronics STM32 System-on-Chip Accelerates Creation of Smart Devices with LoRa® IoT Connections

- Integrates STM32 microcontroller IP and enhanced Semtech radio on one chip

- Ready to connect to LoRa® and other low-power Wide-Area Networks worldwide

- Supported by ST’s rolling 10-year longevity commitment for industrial products

Powering the search for sustainability through smart infrastructure and logistics, smart industry and smart living, STMicroelectronics (NYSE: STM), a global semiconductor leader serving customers across the spectrum of electronics applications, has revealed the world’s first LoRa® system-on-chip (SoC) for connecting smart devices to the Internet of Things (IoT) using long-distance wireless connections.

Powering the search for sustainability through smart infrastructure and logistics, smart industry and smart living, STMicroelectronics (NYSE: STM), a global semiconductor leader serving customers across the spectrum of electronics applications, has revealed the world’s first LoRa® system-on-chip (SoC) for connecting smart devices to the Internet of Things (IoT) using long-distance wireless connections.

The STM32WLE5 SoC lets product developers create devices such as remote environmental sensors, meters, trackers, and process controllers that help efficiently manage energy and resources

Also:

https://www.st.com/en/microcontrollers-microprocessors/stm32wl-series.html

A bit more here

Dev board NUCLEO-WL55JC1

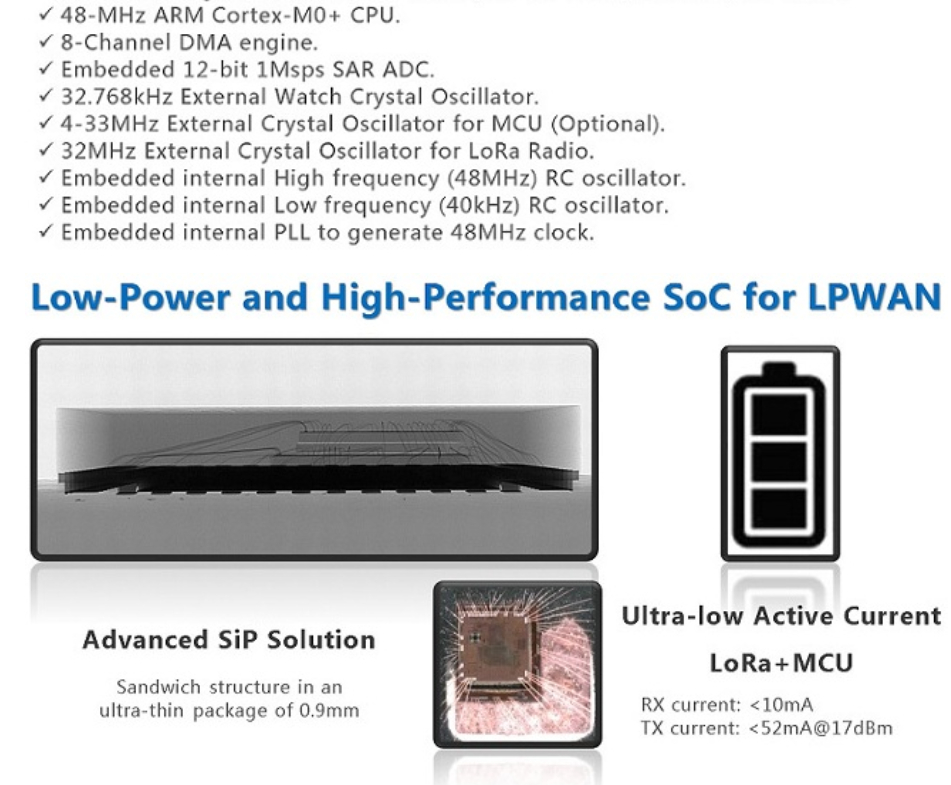

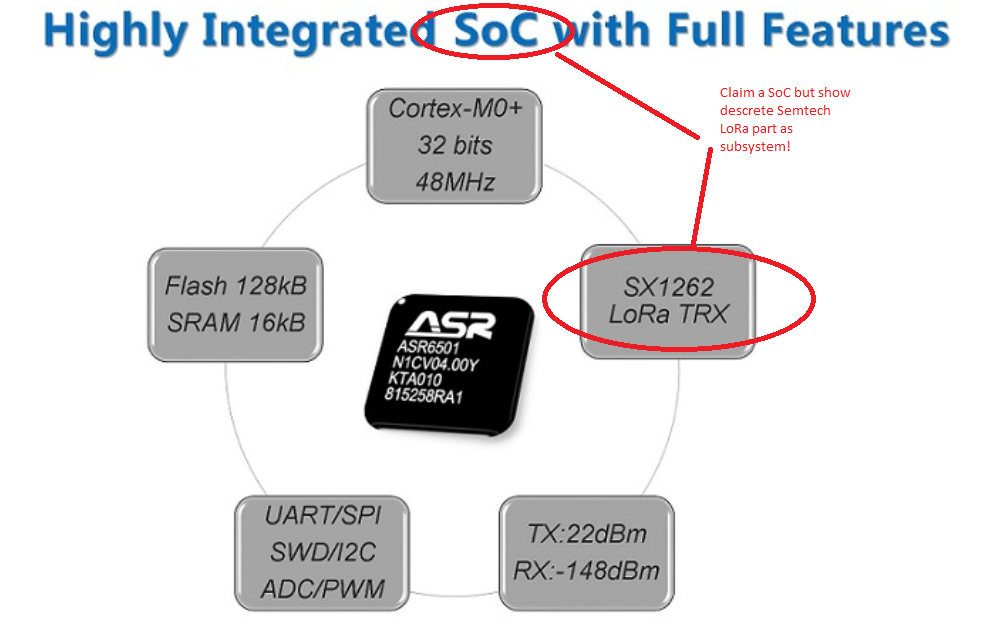

I believe all others todate have been SIP’s (System in Package) vs SOC’s - need to wait and see if their claim that this is MPU + LoRa on single chip is true… if anyone from STM is monitoring and can comment?! Also if they want to send me samples and eval/dev boards?!  Checked e.g. DigiKey, Mouser, Anglia etc yesterday and not even listing NUCLEO-WL55JC1 eval bds let alone having stock yet…

Checked e.g. DigiKey, Mouser, Anglia etc yesterday and not even listing NUCLEO-WL55JC1 eval bds let alone having stock yet…

@bluejedi Despite their description as a SoC the ASR part is by their own admission actually a SIP and they even show a stacked die build photo and use SiP description lower down on the page you link to. This is a common slight of hand played by many ‘chip’ suppliers to the semi industry - SiP not SoC and not just around LoRa but in many other areas…

from ASR website:

Ah, that makes it more clear.

So, the ASR6501 is actually a SIP and not a SoC.

While a SoC is not multi-die nor stacked it does come in a single package which also makes a SoC a ‘System in (a) package’. ![]()

The SoC combines ST’s proven skills in ultra-low-power STM32 microcontroller design with a LoRa-compliant radio in one single-die and easy-to-use device.

‘In one single-die’ would imply SoC.

Has STM provided any evidence that the chip is true single die SoC?

Because in order to integrate ‘hard macro’ of Semtech SX1262 VHDL IP core together with their own one (STM32xxx), the STM have to pay a lot in order to license it first.

It seems to be much more simpler and cheaper to just purchase a wafer from Semtech, separate it onto individual dies, put each one onto micro-PCB together with own die, enclose all the stuff with BGA package…

Just like all other numerous SiP manufacturers do.

STM are one of several who have ‘licensed’ LoRa technology per prior public releases. In this case it is some years ago and given it takes typically 2-4 years to get from IP license to definition, through detailed design, through layout/timing closure/validation and on into initial test silicon before any iterations that can confidently go to production targeted silicon ‘now’ (late 2H’19 through early’21) is about right on timing. They may not necessarily have licened a 'hard macro-block, but potentially a soft macro or even just a higher level definition (VHDL/Verilog/IEEE/Architectural Specification/Definition and associated control API’s for interop and ease of software/stack porting).

Note given licence is several years old it may be that instantiation (be it architectural or detailed specific implementation) is based on earlier SX1272/76/7/8/9 based design efforts rather than latest 126x based design…time will tell. The initial 127x series effectively took a best in class analogue radio family (SX1232/X) and grafted on the LoRa Modem, so it may be STM have done something similar - taken one of their own ‘conventional’ radios and grafted on the LoRa Modem functionality and associated control registers. Again time will tell. Even if using older implementation there is still potential for significant system improvements and power savings as by integrating you have opportunity to e.g. drop I/O drivers, slew rate control, esd protection, shorten trace lengths, speed up inter-functional element comms etc. all reducing power consumption, improving stability and speed of operation and enhancing potential device yield etc. I would suspect licence included at least some planed/proposed improvements and lessons learnt from Gen 1 Semtech Si even if not fully reflecting what SMTC subsequently went on to drop into the SX126x series - so a kind of half way house perhaps?

Targeting Indian Pre-Paid Meter Market?

From your linked STM article:

The integrated radio based on Semtech SX126x IP is engineered with dual high-power and low-power transmitter modes that cover the entire global sub-1GHz unlicensed frequency range from 150MHz to 960MHz, ensuring compatibility with LoRa networks in all territories

good spot…

good spot…

https://lacuna.space/world-premier-first-plant-powered-iot-sensor-sends-signal-to-space/

Look for the demo at upcoming Things Conference, Amsterdam

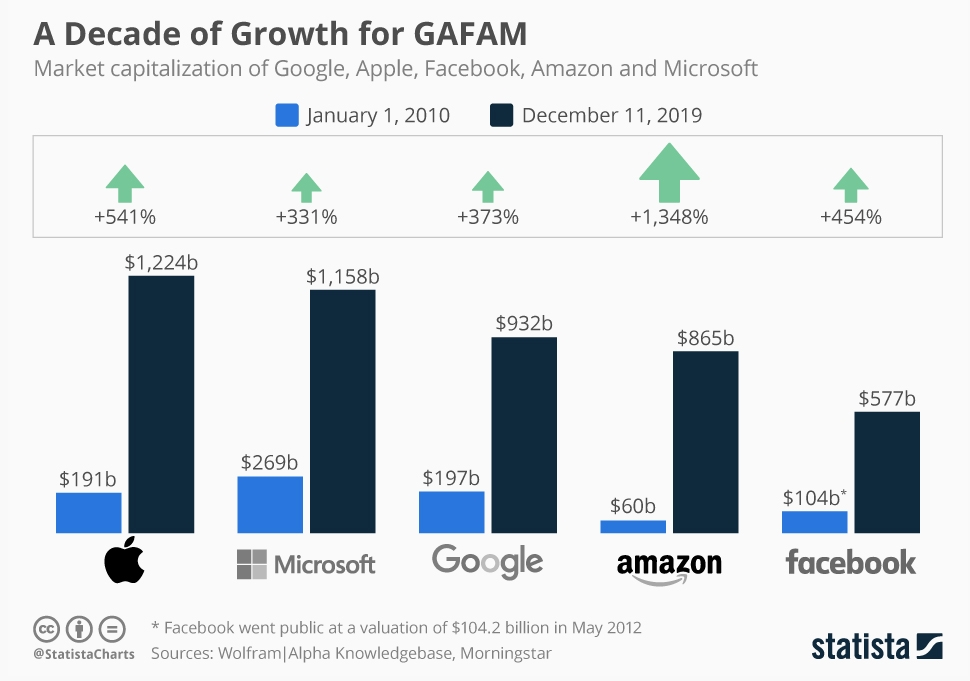

Good visualisation of a decade of growth for the top tech co’s.

Source: https://www.electronicsweekly.com/blogs/mannerisms/markets/how-gafam-grew-2020-01/

Seeeduino XIAO, a cute looking tiny SAMD21 development board.

Key Features

- Powerful CPU: ARM® Cortex®-M0+ 32bit 48MHz microcontroller(SAMD21G18) with 256KB Flash, 32KB SRAM

- Flexible compatibility: Compatible with Arduino IDE

- Easy project operation: Breadboard-friendly

- Small size: As small as a thumb(20x17.5mm) for wearable devices and small projects.

- Multiple development interfaces: 11 digital/analog pins, 10 PWM Pins, 1 DAC output, 1 SWD Bonding pad interface, 1 I2C interface, 1 UART interface, 1 SPI interface.

Euridis Association (Euridis), an international nonprofit industry association promoting the development of standard protocols, such as device language message specification (DLMS) over low power wide area networks (LPWAN) for the utility industry