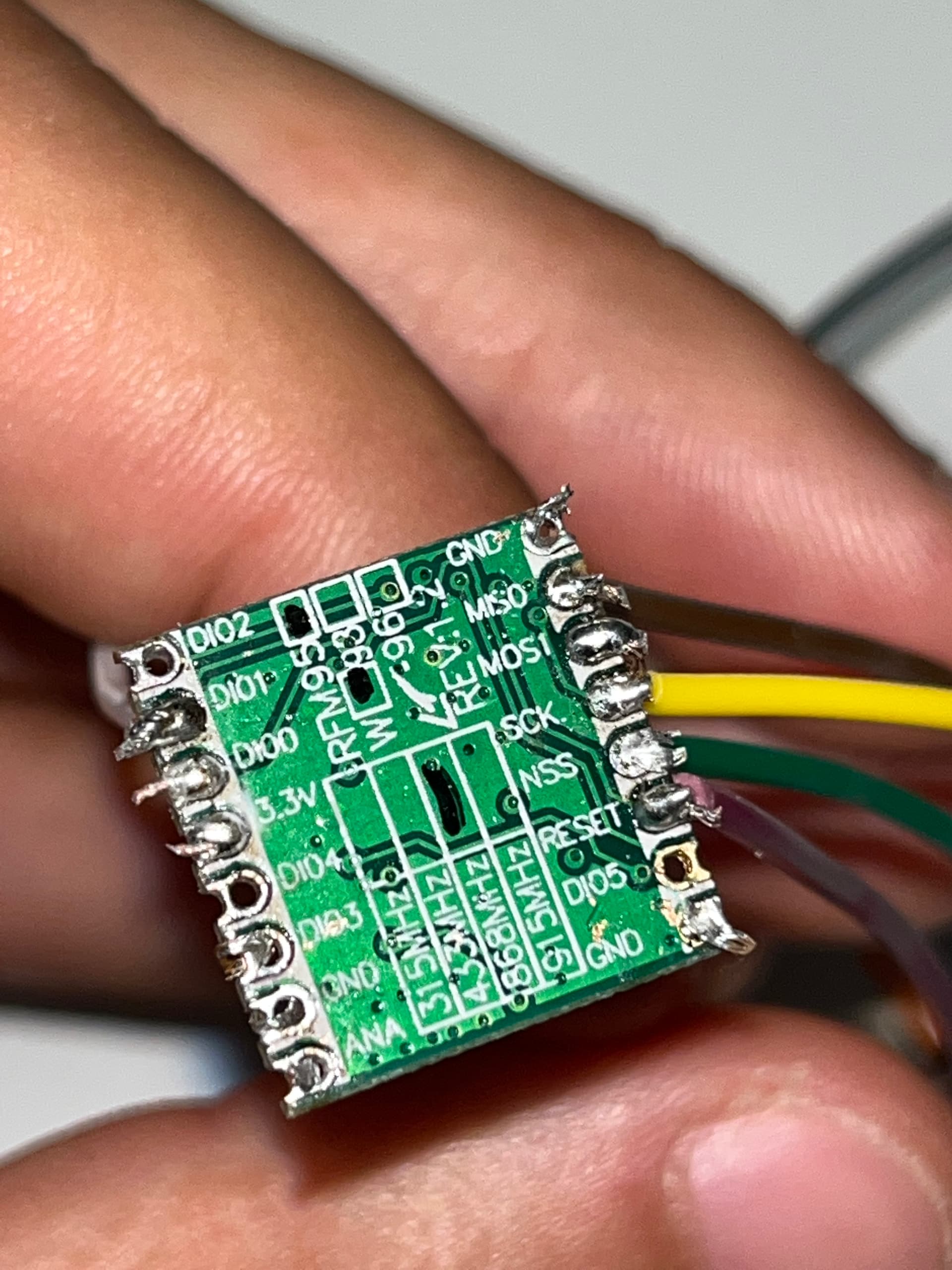

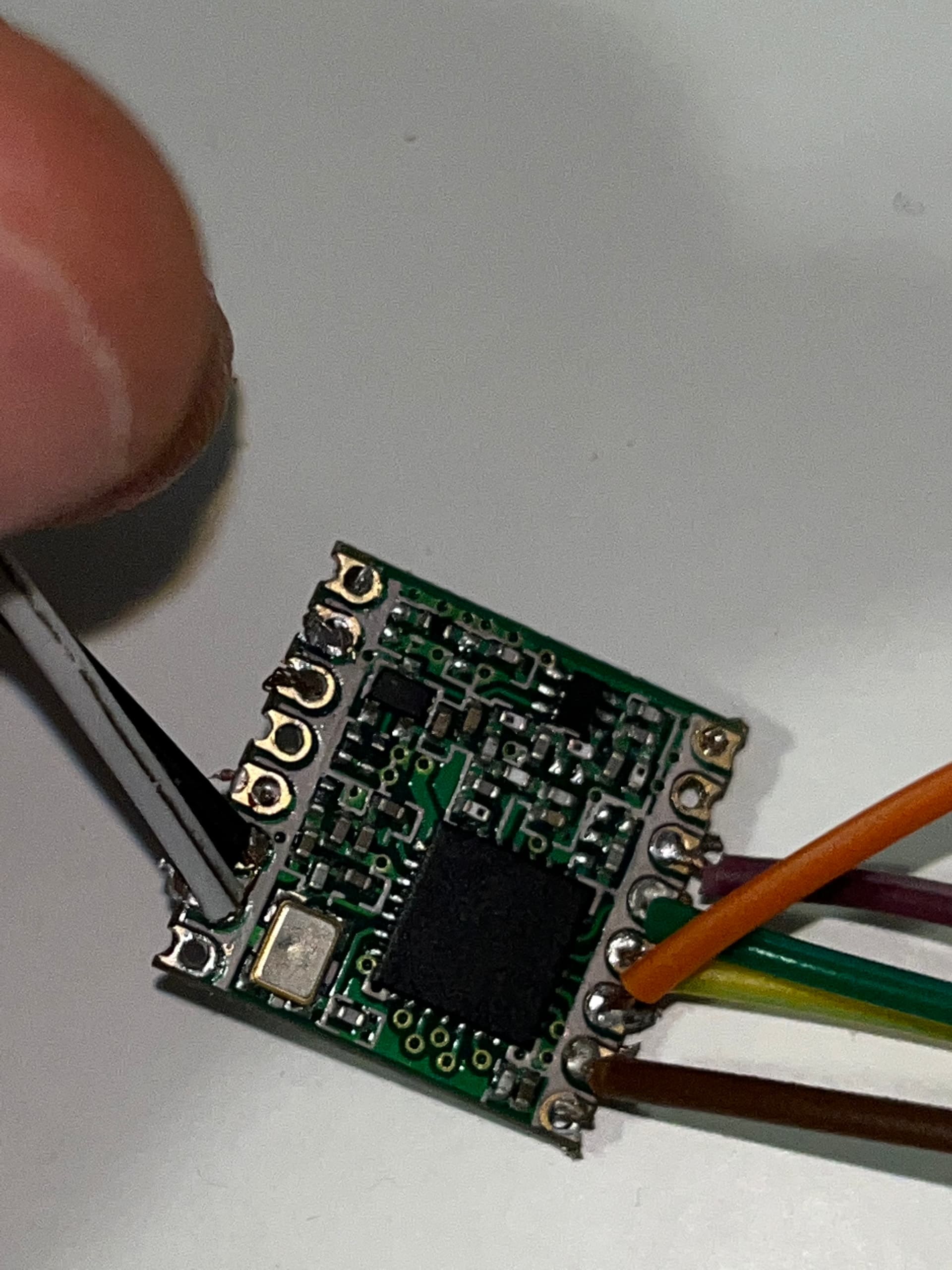

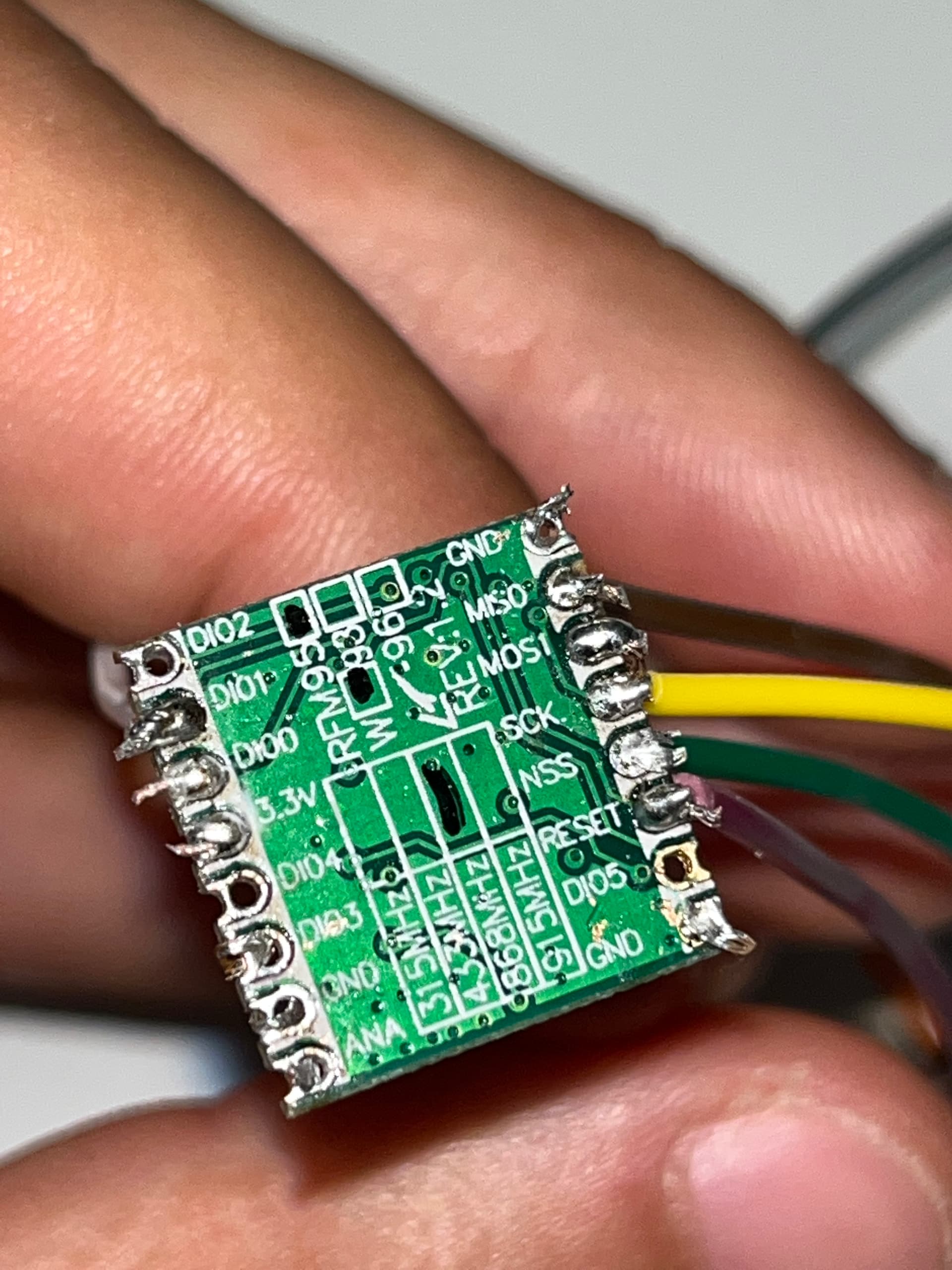

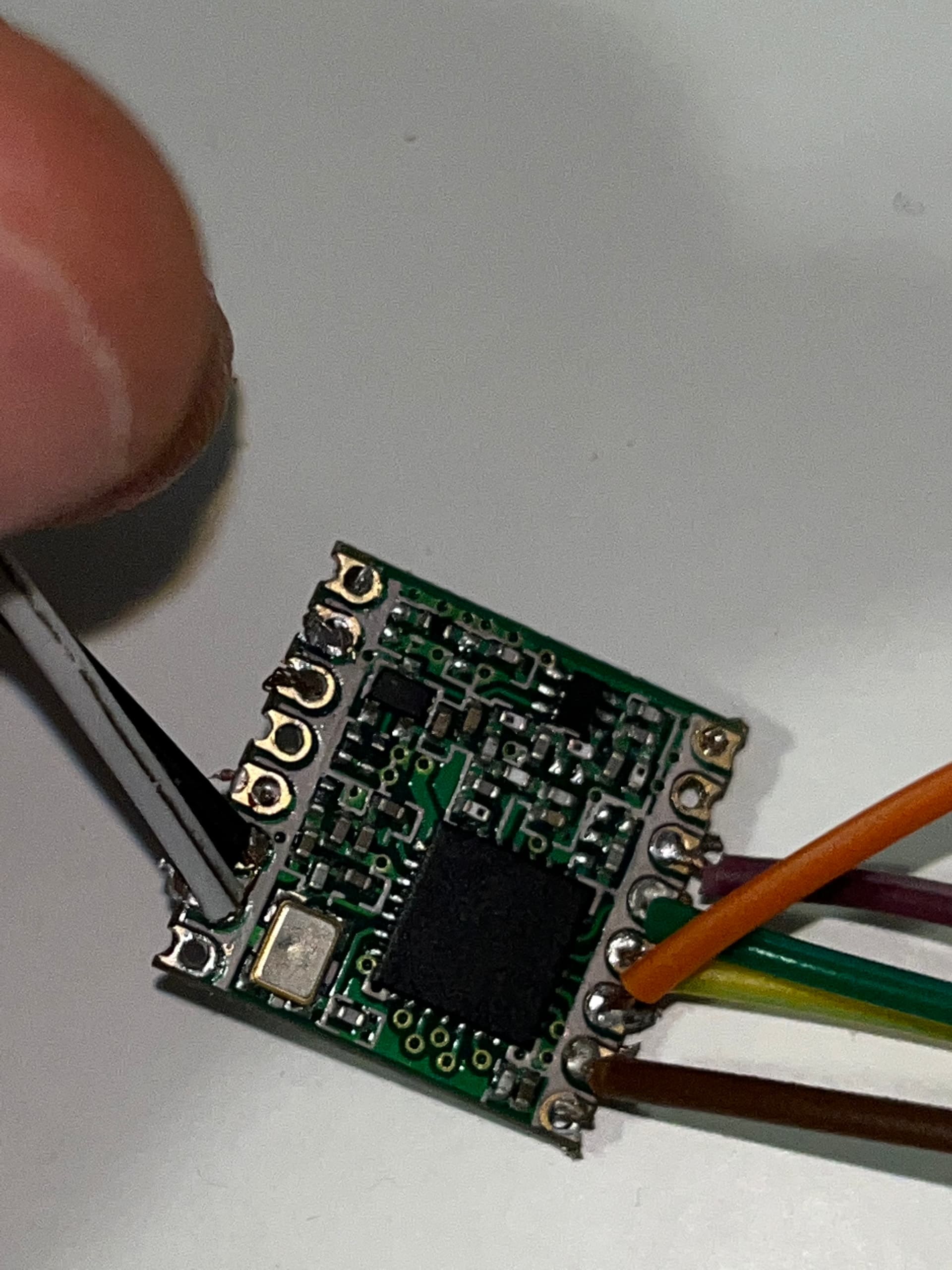

Eeeehm, nope. I am not using a logic level converter… I saw video on youtube of people not using it… By the way, I also have a Hope LoRa module, but I think I’ve damaged it.

Eeeehm, nope. I am not using a logic level converter… I saw video on youtube of people not using it… By the way, I also have a Hope LoRa module, but I think I’ve damaged it.